En una reciente y deslumbrante mañana en California (EE.UU.), la investigadora del MIT Vivienne Sze subió a un pequeño escenario para realizar la que quizá haya sido presentación más desconcertante de su carrera. Dominaba el tema a la perfección. Debía hablar sobre los chips que se desarrollan en su laboratorio y de cómo iban a acercar el poder de la inteligencia artificial (IA) a una multitud de dispositivos con una potencia limitada sin tener que depender de los enormes centros de datos donde se realizan la mayoría de los cálculos de IA. Pero, tanto lo que vio en la conferencia como el público que acudió la hicieron reflexionar.

Hablamos de MARS, una conferencia de élite, solo para invitados, en la que los robots pasean (o vuelan) por un resort de lujo, mezclándose con famosos científicos y autores de ciencia ficción. Solo unos pocos investigadores fueron invitados a dar charlas técnicas, y las sesiones tienden a ser tanto inspiradoras como esclarecedoras. El público estaba compuesto por unos 100 investigadores, directores ejecutivos y algunos de los empresarios más importantes del mundo. El maestro de ceremonias de MARS fue el fundador y presidente de Amazon, Jeff Bezos, que estaba sentado en la primera fila. «Se podría decir que era un público de muy alto nivel», recuerda Sze con una sonrisa.

Otros ponentes de MARS presentaron robots que cortan al estilo kárate, drones que aletean como si fueran grandes insectos extrañamente silenciosos, e incluso proyectos para crear colonias marcianas. Ante esta competencia, los chips de Sze podían parecer más modestos. A simple vista, no se distinguen de los chips que hay dentro de cualquier dispositivo electrónico. Sin embargo, sus microprocesadores eran indudablemente mucho más importantes que cualquier otra cosa que hubo en la conferencia.

Nuevas capacidades

Los nuevos diseños de chips, como los que se desarrollan en el laboratorio de Sze, pueden ser cruciales para el futuro progreso de la IA, y los drones y robots que se dejaron ver en MARS. Hasta ahora, el software de IA se ejecutaba principalmente en unidades de procesamiento gráfico (GPU, por sus siglas en inglés), pero los nuevos diseños especializados de hardware podrían lograr que los algoritmos de IA sean más potentes, lo que abriría el camino a unas nuevas aplicaciones. Los nuevos chips de inteligencia artificial podrían masificar los robots de almacén y permitir que los teléfonos inteligentes crean escenarios fotorrealistas de realidad aumentada.

Los diseños de los chips de Sze son muy eficientes y flexibles, algo crucial para un campo que evoluciona tan rápido como la IA (ver ¿Quién ganará la batalla de los chips si el sector de la IA no para de cambiar?). En concreto, están diseñados para exprimir aún más potencial de los algoritmos de aprendizaje profundo que ya han revolucionado el mundo. Este proceso incluso podría lograr que este tipo de programas evolucionen por sí solos. Sze detalla: «Dado que la ley de Moore se ha ralentizado, necesitamos un nuevo hardware».

Esta ley choca cada vez más con los límites físicos de los componentes de ingeniería a escala atómica. Y está despertando un creciente interés en arquitecturas alternativas y nuevos enfoques de computación.

Este interés ha llegado incluso al Gobierno de EE. UU., que además de mantener su liderazgo en el diseño de chips en general, confía en los microprocesadores especializados para arrebatarle a China el trono de la IA. De hecho, los propios chips de Sze se están creando gracias a fondos de un programa de DARPA destinado a ayudar a desarrollar nuevos diseños de chips de IA (ver Así es la estrategia de EE.UU. para quitarle a China el trono de la IA).

Pero el impulso en la innovación de la fabricación de chips procede principalmente del aprendizaje profundo, una técnica muy poderosa de enseñar a las máquinas a realizar tareas útiles. En vez de dar a un ordenador un conjunto de reglas a seguir, una máquina se programa a sí misma básicamente. Los datos de entrenamiento se introducen en una gran red neuronal artificial simulada, que luego se ajusta para que produzca el resultado deseado. Con suficiente entrenamiento, un sistema de aprendizaje profundo puede encontrar patrones sutiles y abstractos en los datos. La técnica se aplica a una creciente variedad de tareas prácticas, desde el reconocimiento facial en los teléfonos inteligentes hasta la predicción de enfermedades a partir de imágenes médicas.

La carrera de los chips de IA

El aprendizaje profundo no depende tanto de la ley de Moore. Las redes neuronales ejecutan muchos cálculos matemáticos en paralelo, un enfoque para el que los GPU de videojuegos resultan mucho más efectivos dado que realizan computación paralela para renderizar imágenes en 3D. Pero los microchips diseñados específicamente para el aprendizaje profundo deberían ser aún más potentes.

El potencial de las nuevas arquitecturas de chips para mejorar la inteligencia artificial ha impulsado la actividad empresarial a un nivel que la industria de los chips no ha visto en décadas (ver La nueva carrera de los chips de silicio se libra en el cuadrilátero de la inteligencia artificial y China da la vuelta al marcador de los chips gracias a la IA). Las grandes empresas tecnológicas que quieren aprovechar y comercializar la inteligencia artificial, como Google, Microsoft y (sí) Amazon, están trabajando en sus propios chips de aprendizaje profundo. Pero también hay muchas start-ups trabajando en este campo. De hecho, el analista de microchips en la empresa de analistas Linley Group Mike Delmer considera que «es imposible hacer un seguimiento de todas las compañías que están apareciendo en el espacio del chip de IA». Y añade: «No bromeo cuando digo que descubrimos un nuevo chip casi cada semana«.

La verdadera oportunidad, según Sze, no reside en construir los chips de aprendizaje profundo más poderosos. La eficiencia energética también es importante porque la IA también debe funcionar más allá de los grandes centros de datos, lo que significa que los microprocesadores deberían ser capaces de funcionar con la energía disponible en el dispositivo. Esto se conoce como operar «al límite».

«La IA estará en todas partes, así que es importante encontrar formas de aumentar la eficiencia energética«, afirma el vicepresidente del grupo de productos de inteligencia artificial de Intel, Naveen Rao. Por ejemplo, el hardware de Sze es más eficiente, en parte, porque reduce físicamente el atasco entre el lugar en el que almacenan los datos y aquel en el que se analizan, pero también porque utiliza esquemas inteligentes para reutilizar los datos. Antes de unirse al MIT, Sze fue pionera en este enfoque para mejorar la eficiencia de la compresión de vídeo en Texas Instruments.

En un campo que avanza tan rápido, como es el aprendizaje profundo, el desafío para aquellos que trabajan con chips de IA consiste en asegurarse de que sean lo suficientemente flexibles para adaptarse a cualquier aplicación. Es fácil diseñar un chip súper eficiente capaz de hacer solo una tarea, pero ese tipo de producto se volverá obsoleto rápidamente.

El chip de Sze se llama Eyeriss. Desarrollado en colaboración con el científico investigador de Nvidia y profesor del MIT, Joel Emer, fue probado junto con varios procesadores estándar para ver cómo manejaba diferentes algoritmos de aprendizaje profundo. Equilibrando la eficiencia con la flexibilidad, el rendimiento del nuevo chip alcanza resulta entre 10 e incluso 1.000 veces más eficiente que el hardware existente, según un artículo publicado el año pasado.

Foto: Los investigadores del MIT Sertac Karaman y Vivienne Sze desarrollaron el nuevo chip.

Los chips de IA más simples ya están generando un gran impacto. Los teléfonos inteligentes de gama alta ya incluyen chips optimizados para ejecutar algoritmos de aprendizaje profundo para el reconocimiento de imagen y voz. Los chips más eficientes podrían permitir que estos dispositivos ejecuten un código de IA más potente con mejores capacidades. Los coches autónomos también necesitan poderosos chips de IA, ya que la mayoría de los prototipos dependen actualmente de un montón de ordenadores dentro del maletero.

Rao sostiene que los chips del MIT parecen prometedores, pero son muchos los factores que determinarán si una nueva arquitectura de hardware tendrá éxito. Uno de los más importantes, según él, es el desarrollo de software que permita a los programadores ejecutar código en él. «Hacer algo útil para aquellos que lo elaboran es probablemente el mayor obstáculo para la adopción», explica.

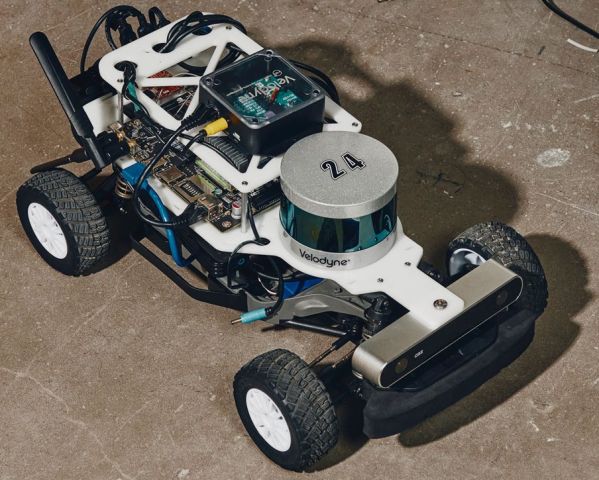

De hecho, el laboratorio de Sze también explora formas de diseñar software para explotar mejor las propiedades de los chips informáticos existentes. Y este trabajo se extiende más allá del aprendizaje profundo. Junto con el investigador del Departamento de Aeronáutica y Astronáutica del MIT Sertac Karaman, Sze desarrolló un chip de bajo consumo llamado Navion que realiza mapas en 3D y navegación de manera increíblemente eficiente, lo que permite integrarlo en un pequeño dron. Para este esfuerzo fue crucial diseñar un chip capaz de explotar el comportamiento de los algoritmos de navegación y crear un algoritmo que puediera aprovechar al máximo este chip personalizado. Junto al desarrollo del aprendizaje profundo, Navion refleja la forma en la que el software y el hardware de IA empiezan a evolucionar en simbiosis.

Los chips de Sze quizás no son tan llamativos como un dron con alas, pero el hecho de que fueran presentados en MARS refleja lo importante que será su tecnología, y la innovación del silicio en general, para el futuro de la IA. Después de su presentación, Sze afirma que algunos de los otros ponentes expresaron su interés en conocer más. «La gente encontró muchos casos importantes de aplicación», concluye. En otras palabras, podemos esperar que en la próxima conferencia de MARS los robots y drones lleven dentro algo bastante más especial.

Artículos relacionados:

■ Un robot que procura moverse tan bien como una hormiga

■ Chips de potencia ultra baja ayudan a hacer robots pequeños más capaces

■ Chip de cómputo basado en luz funciona similar a las neuronas